Vyomex Digital Oscillator IP Core v1.0 (Proprietary)

Overview

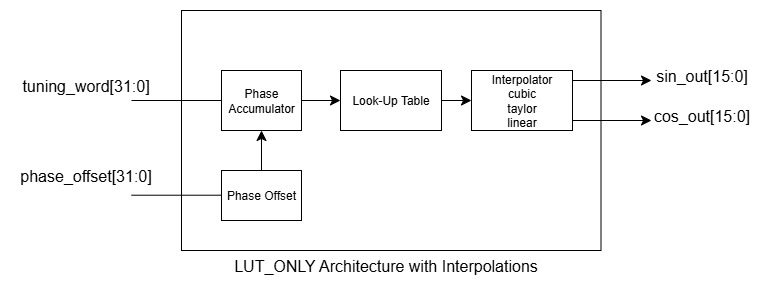

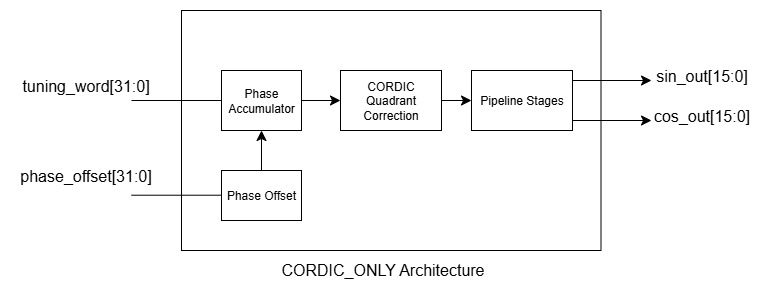

Vyomex Digital Oscillator IP Core is a reusable, configurable CORDIC+LUT-based waveform generator for FPGA/ASIC DSP systems.

It supports programmable sine/cosine outputs, radix-2, radix-4, and radix-8 CORDIC algorithms, and features AXI4-Lite and SPI interfaces for easy integration.

Applications

- Software Defined Radio (SDR)

- Radar and Sonar waveform generation

- Communication baseband processors

- Test & Measurement instruments

- Embedded DSP systems

Key Features

- CORDIC-based oscillator with LUT initialization

- Radix-2/4/8 pipeline option

- 16-bit configurable output precision (

sfixed_t format)

- 32-bit frequency tuning word for ultra-fine control

- AXI4-Lite and SPI interfaces

- Programmable phase and amplitude

- Signed fixed-point sine and cosine outputs

- No DSP/BRAM usage for resource efficiency in CORDIC_ONLY mode

- Fully synthesizable RTL, simulation validated in Xilinx Vivado

Interfaces & Ports

| Port Name | Dir | Width | Description |

|---|

| sys_clk | In | 1 | System clock for DDS core |

| sys_rst | In | 1 | Active-high system reset |

| ce | In | 1 | Clock enable for DDS accumulator |

| S_AXI_ACLK | In | 1 | AXI4-Lite clock |

| S_AXI_ARESETN | In | 1 | AXI4-Lite reset (active low) |

| S_AXI_AWADDR | In | 4 | Write address |

| S_AXI_AWVALID | In | 1 | Write address valid |

| S_AXI_AWREADY | Out | 1 | Write address ready |

| S_AXI_WDATA | In | 32 | Write data |

| S_AXI_WSTRB | In | 4 | Write strobes |

| S_AXI_WVALID | In | 1 | Write valid |

| S_AXI_WREADY | Out | 1 | Write ready |

| S_AXI_BRESP | Out | 2 | Write response |

| S_AXI_BVALID | Out | 1 | Write response valid |

| S_AXI_BREADY | In | 1 | Write response ready |

| S_AXI_ARADDR | In | 4 | Read address |

| S_AXI_ARVALID | In | 1 | Read address valid |

| S_AXI_ARREADY | Out | 1 | Read address ready |

| S_AXI_RDATA | Out | 32 | Read data |

| S_AXI_RRESP | Out | 2 | Read response |

| S_AXI_RVALID | Out | 1 | Read valid |

| S_AXI_RREADY | In | 1 | Read ready |

| spi_sclk | In | 1 | SPI serial clock |

| spi_mosi | In | 1 | SPI master-out, slave-in |

| spi_miso | Out | 1 | SPI master-in, slave-out |

| spi_cs_n | In | 1 | SPI chip select (active low) |

| sin_out | Out | sfixed_t (18-bit) | Sine output (signed fixed-point) |

| cos_out | Out | sfixed_t (18-bit) | Cosine output (signed fixed-point) |

| valid_out | Out | 1 | Output data valid flag |

SPI Register Map

| Address | Name | Width | Notes |

|---|

| 0x00 | CTRL | 8 | =Enable, [1]=Reset, [2]=SrcSel |

| 0x01 | TUNING_WORD[7:0] | 8 | LSB first |

| 0x02 | TUNING_WORD[15:8] | 8 | |

| 0x03 | TUNING_WORD[23:16] | 8 | |

| 0x04 | TUNING_WORD[31:24] | 8 | MSB |

| 0x05 | PHASE[7:0] | 8 | |

| 0x06 | PHASE[15:8] | 8 | |

| 0x07 | PHASE[23:16] | 8 | |

| 0x08 | PHASE[31:24] | 8 | |

| 0x09 | AMPL[7:0] | 8 | |

| 0x0A | AMPL[15:8] | 8 | |

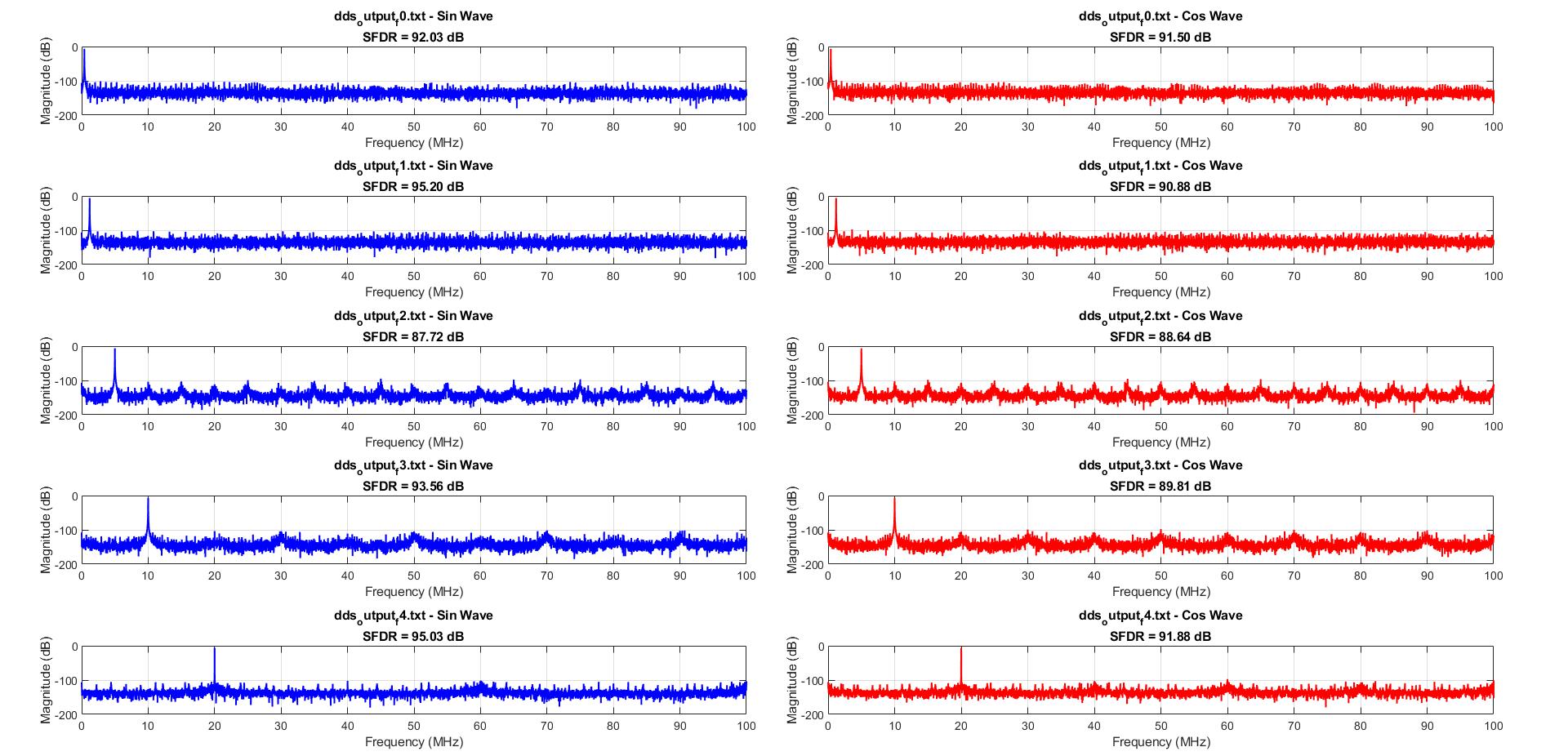

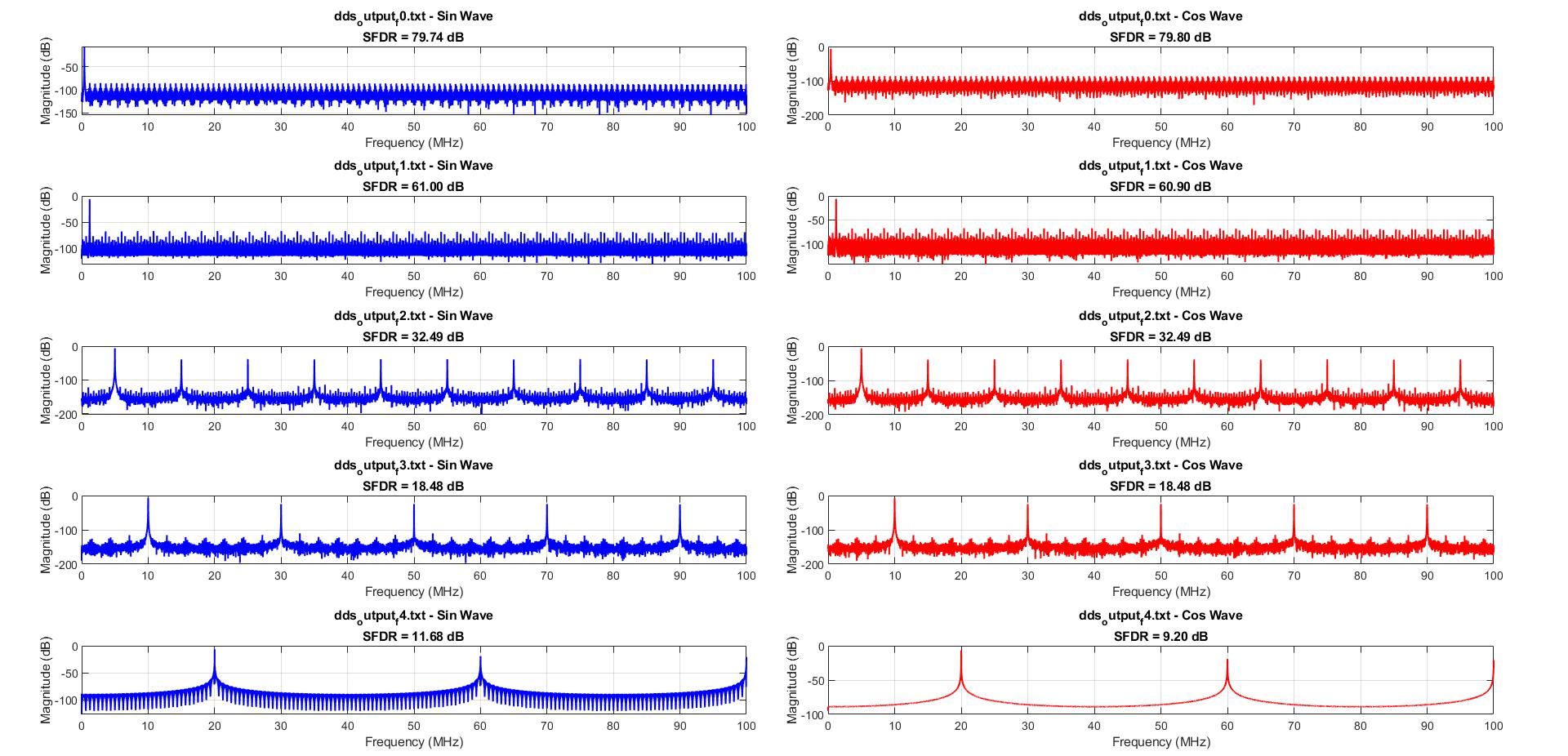

Performance Metrics

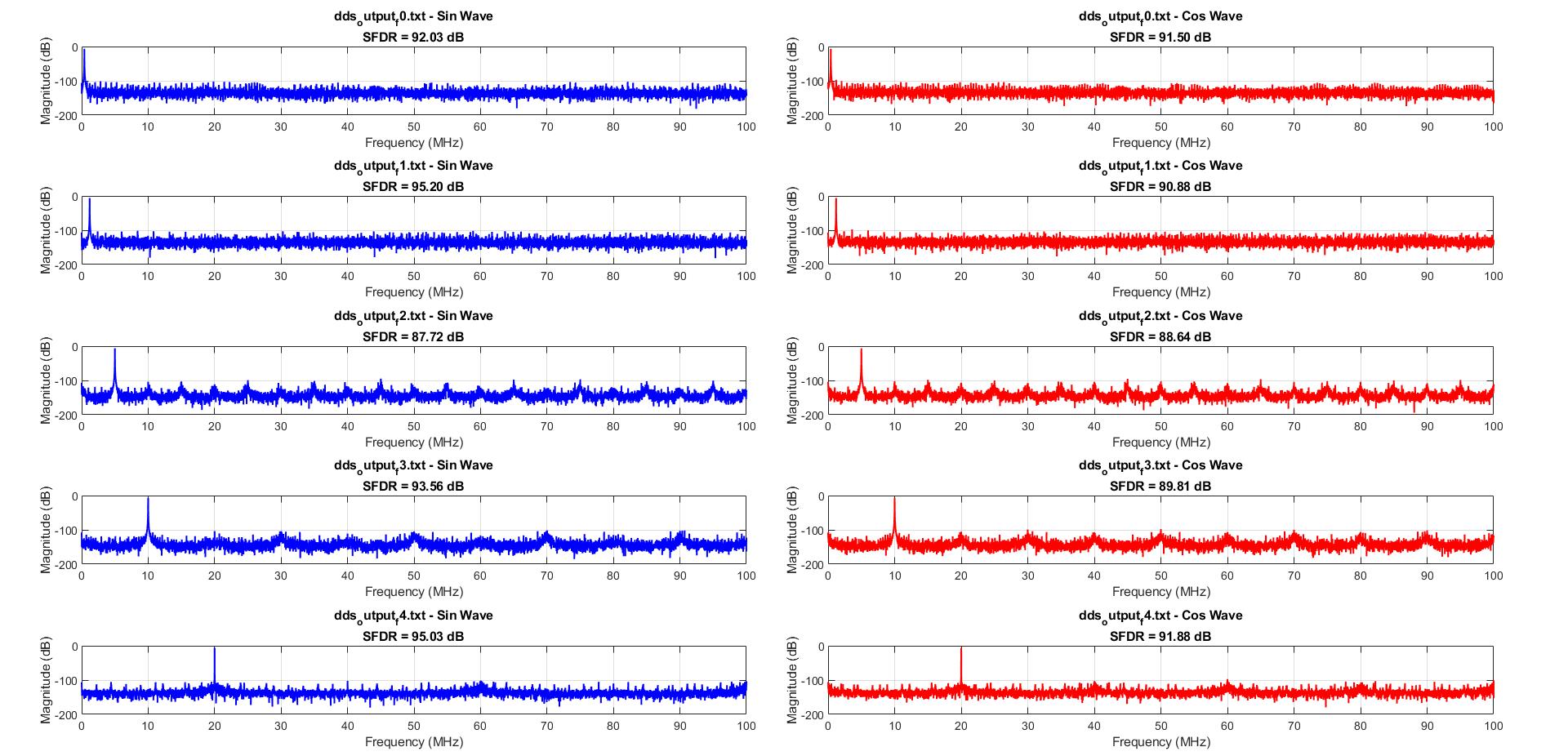

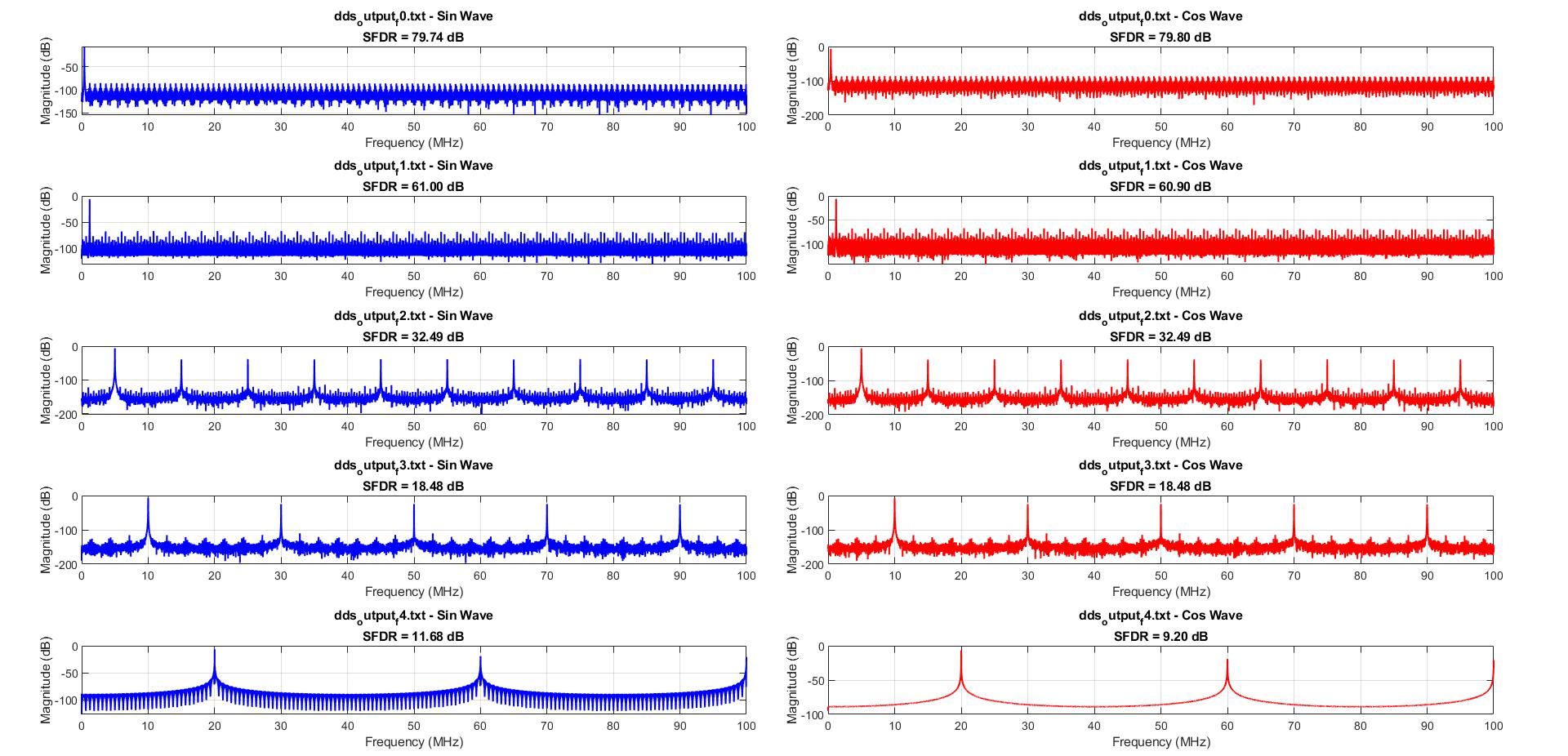

f0=400kHz,f1=1.2MHz,f2=5MHz,f3=10MHz,f4=20MHz,fclk=200MHz

CORDIC Only (Radix-2 / Radix-4)

| Frequency Index | SFDR (sin / cos) [dB] | THD [dB] |

|---|

| f0 | 92.03 / 91.50 | -96.97 / -93.04 |

| f1 | 95.20 / 90.88 | -92.44 / -88.95 |

| f2 | 87.72 / 88.64 | -92.59 / -90.50 |

| f3 | 93.56 / 89.81 | -94.44 / -91.85 |

| f4 | 95.03 / 91.88 | -92.04 / -90.09 |

LUT + 4-Point Cubic Interpolation

| Frequency Index | SFDR (sin / cos) [dB] | THD [dB] |

|---|

| f0 | 79.74 / 79.80 | -83.22 / -83.40 |

| f1 | 61.00 / 60.90 | -57.75 / -57.69 |

| f2 | 32.49 / 32.49 | -32.61 / -32.61 |

| f3 | 18.48 / 18.48 | -26.56 / -26.56 |

| f4 | 11.68 / 9.20 | -10.08 / -11.32 |

Resource Utilization

| Resource Type | LUT+CUBIC | CORDIC_ONLY | Notes |

|---|

| LUT | 4837 | 2644 | Can be Optimized with interpolation and LUT definitions |

| Flip-Flop (FF) | 758 | 2226 | |

| DSP | 34 | 0 | DSP-free architecture for CORDIC and Taylor Interpolations |

| BRAM | 0 | 0 | LUT-only, no BRAM |

| URAM | 0 | 0 | Not required |

Verification

- Top-level testbenches for AXI and SPI interfaces

- DDS-level testbench for sine/cosine waveform accuracy

- Validated via simulation in Xilinx Vivado

Deliverables

- RTL Source Codes (VHDL)

- Testbench Files (VHDL)

- Performance Analysis Scripts (MATLAB)

- Documentation (Datasheet, Release Notes, Register Map)

Ordering Information

- Product: Vyomex Digital Oscillator IP Core v1.0

- Delivery: VHDL source, testbenches, documentation

- License: Proprietary — Vyomex

- Support: support@vyomex.in